-

Notifications

You must be signed in to change notification settings - Fork 229

How to simulate your design in ISE

-

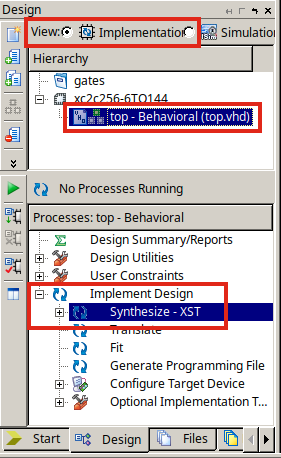

To synthesize (compile) your design, select Implementation view, choose source file in Hierarchy part

top - Behavioral (top.vhd), expand Implement Design in Processes window, and double click on Synthesize - XSL.

-

If process "Synthesize - XST" completed successfully, create a new source file to specify test cases Project > New Source... > VHDL Test Bench with file name

top_tb00, and click on buttons Next >, Next >, Finish.In

top_tb00.vhdtemplate file comment all parts dealing with<clock>_period. (We are going to use synchronous clock processes later.)

--line 64

-- constant <clock>_period : time := 10 ns;--lines 78 to 84

-- -- Clock process definitions

-- <clock>_process :process

-- begin

-- <clock> <= '0';

-- wait for <clock>_period/2;

-- <clock> <= '1';

-- wait for <clock>_period/2;

-- end process;--line 93

-- wait for <clock>_period*10;In the last process stim_proc specify all test cases to simulate before final wait; statement. Basically, test case is a set of input values for your design, while simulator will generate proper outputs.

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

-- wait for <clock>_period*10;

-- insert stimulus here

BTN1 <= '0'; BTN0 <= '0'; wait for 100 ns;

BTN1 <= '0'; BTN0 <= '1'; wait for 100 ns;

BTN1 <= '1'; BTN0 <= '0'; wait for 100 ns;

BTN1 <= '1'; BTN0 <= '1'; wait for 100 ns;

wait;

end process;Note, one-bit values are specified by apostrophes. Do not forget to pause the simulator after each test case by wait for statement. Save all files in menu File > Save All.

-

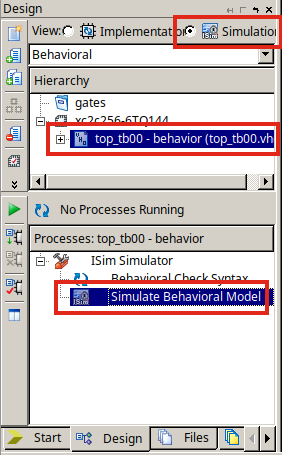

To run the simulation, switch Simulation view (above the Hierarchy part), choose

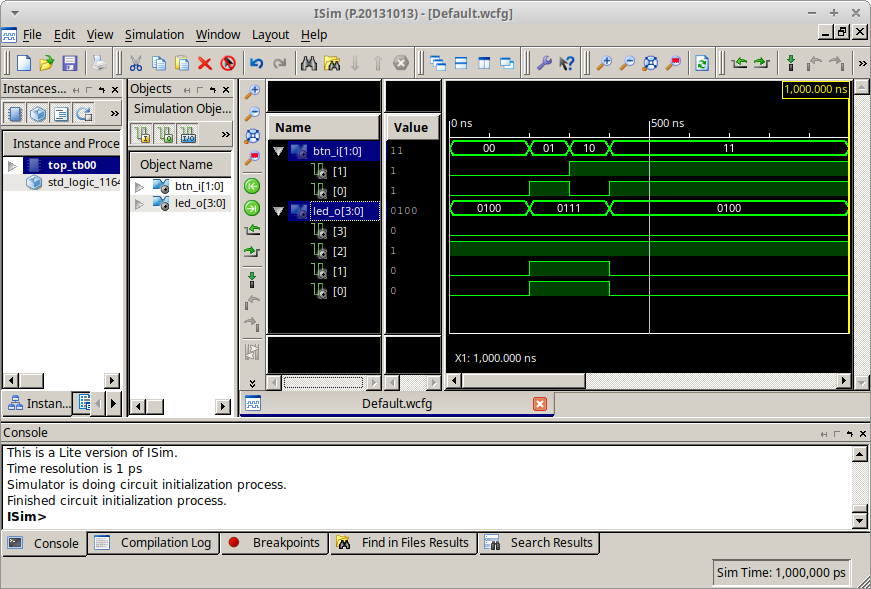

top_tb00 - behavior (top_tb00.vhd)line in Hierarchy part, expand ISim Simulator in Processes window, and double click on Simulate Behavioral Model. The new window with all waveforms will appear.

To zoom the view, choose command from menu View > Zoom > To Full View F6.